PMOS FAB Process Flow 에 대해 이해하기 (Front 공정

수율 개선 업무 및 불량 분석 업무를 진행 하기에 앞서, 신입 사원 들은 FAB Process Flow 에 대해 먼저 학습 하게 된다.

하지만 실제 FAB 에서 사용하는 FAB Process는 취업 준비생들이 먼저 습득 하기엔 조금 무리가 있다고 생각이 되어 진다.

따라서 오늘 포스팅 글은 Active 소자인 NMOSFET의 기본 FAB Process FLow에 대해서 요약을 해보도록 하겠다.

우선 반도체 설계팀에서는 주로 아래와 같은 Schematic 기호를 사용 하게 설계를 진행 한다. 하나의 반도체 Chip에 수백만개의 Active 소자와 (NMOS, PMOS..) Passive 소자(Resistor, Capacitor) 가 직접 되어 있는데, 이렇게 간단한 기호를 사용 하지 않으면 설계 하는데 상당한 시간이 소요 될 것이다.

하지만 잘 생각 해보면, FAB 공정을 통해 우리가 이러한 모양의 NMOS FET을 어떻게 만들지? 라는 의문이 많이 들 것이다. 그래서 또다른 반도체 설계 부서인 Layout Engineer 들이 이러한 Schematic 구조의 설계도를 반도체 FAB에서 생산이 가능 하게 Layout 화를 시켜 준다.

우리와 같은 FAB Engineer 들은 일련의 FAB Process 공정 진행 순서를 통해 실리콘 웨이퍼 표면에 아래와 같은 Layout을 똑같이 만들어 줄 수 있도록 Photo, Deposition, Etch, IMP 공정의 일련의 순서 배치를 통해 공정을 진행 한다 라고 이해 하면 된다. 즉 우리가 실제로 반도체 Chip 을 Micro scope 와 같은 현미경으로 확대 해서 보거나, SEM 분석 장비를 통해서 확대 시켜 보게 되면 위의 Schematic 구조가 보이는 것이 아니라 아래와 같은 NMOS Layout 이 보이게 되는 것이다.

우리가 위의 NMOS Layout 이미지로 Wafer 를 위에서 아래로 내려보는 평면도에 대한 이해가 되었다면 이제는 FAB Process FLOW를 공부 하기 위하여 붉은색 실선으로 잘랐다고 생각을 하고 단면도가 어떻게 생긴지 공부 해 보도록 해보자.

Wafer 표면에 위의 그림과 같은 규소 산화막 (SiO2) 를 형성 시킨다.

Initial Oxidation 진행 하는 이유는 후속 공정에 있을 IMP 공정에 대비한 Buffer (방어막) 역할을 해 준다고

쉽게 이해 하면 될 것 같습니다. Ion IMPLANT 공정은 Wafer 표면이 아닌 높은 에너지와 온도를 사용 하여

Wafer 깊숙히 IMPlanting을 진행 해야 하기 때문에, Silicon 표면 보호를 위해 Deposition 한다고 이해 하시면 될 것 같습니다.

Buffer 산화막을 증착 시킨 뒤에, 우리는 Nitride란 금속 물질을 Wafer 표면 위에 Deposition 하게 됩니다.

Nitride를 증착 시켜주는 이유는 후속 공정인 Well 을 형성 하기 위해 Etching 공정을 진행 하게 되는데,

이 때에 막질이 단단한 Nitride를 증착 시켜 주어서 또한 Blocking 역할을 해 주는 역할을 진행 하게 됩니다.

항상 우리가 원하는 Pattern을 만들기 위해서는, Photo 공정을 통해 Pattering 작업을 진행 해야 합니다.

사전 단계로 Photo resistor 라는 빛을 받으면 물러져 녹아 없어지는 Positive PR과 반대로 빛을 받으면 단단하게 굳어지는 네거티브 PR이 있는데, 여기서는 Positive PR로 설명을 하고, 이 Positive PR을 먼저 Deposition 한 후에 우리가 사용할 Photo mask를 통해 Patterning 할 부분만 Open 시켜 주게 됩니다.

위의 이미지와 같이 n-well photo mask를 웨이퍼 위에 놓고 자외선을 쪼이게 되면 마스크 크롬이 있는

부분은 빛이 통과하지 못하고, 크롬이 없는 부분은 빛이 통과 하게 되어 빛에 쪼인 PR 들은 물렁물렁 하게 되고 빛에 쪼이지 않는 PR 들은 단단하게 되어 웨이퍼에 남아 있다.

즉 이 과정을 development 과정이라고 하고 우리가 Patterning 을 원하는 부분만 할 수 있도록 할 수 있게 한다. 다음 Exposure 과정을 통하여 우리가 Patterning 원하는 부분의 PR은 제거가 된다.

N-well Mask를 사용 하여 Develop, Exposure가 끝나게 되면 해당 영역에 PR은 제거가 되고, Etch 공정을

진행 하게 된다. Etching 공정엔 Dry, Wet Etch 두 종류가 있는데 Dry Etching 같은 경우엔 조금 더 정교하게 식각을 할 필요가 있는 부분에 진행을 하고, 상대적으로 덜 정교해도 되는 부분은 Wet Etching을 사용 하게 된다.

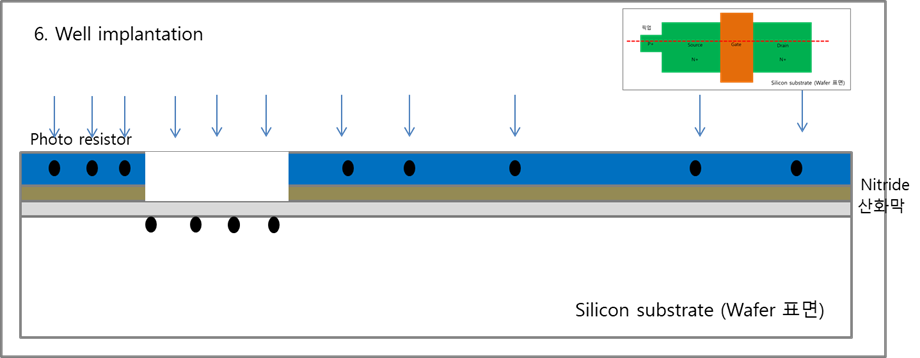

NMOS를 형성 하기 위해, N-Well 을 형성 시킬 부분에는 인(P) 과 같은 5족 원소인 n-type 불순물을 주입 시킨다. 이 떄에 PR과 Nitride 가 있는 영역은 Blocking 이 되어 IMPLANT가 되지 않고, N-Well Mask를 통해

PR을 제거 해 준 영역만 침투 하여 Implant가 진행 된다. Implant란 말은 치과에서 많이 들어보셨을 텐데 심는 다는 뜻으로, 웨이퍼 표면에 씨앗을 뿌리듯 불순물을 심는다는 의미이다.

Nitride위에 덮여 있는 PR을 제거 해준다. 보통 PR은 C(탄소) 가 주성분인데 Strip 공정에서는 O2 (산소)를

주입 시켜 CO2로 제거 할 수 있도록 공정이 진행 된다.

IMPLANT 공정을 통해 주입된 불순물들은 위의 그림과 같이 Wafer 표면에만 주입이 되어 있는데, 이것들을

원하는 깊이 만큼 분포시키기 위하여 수시간 동안 수백 도의 높은 온도로 가열 하여, 농도 차에 의해 확산을 시켜 n-well을 형성 시킨다.

Mosfet의 전극의 역할을 해주는 Poly 물질을 Deposition 해 준다. Poly 는 전도성 (전기를 흐르게 해주는 정도)가 낮아 전도성을 높여 주기 위하여 인과 같은 5족 원소, 즉 n-type의 불순물을 도핑 시킨다. 폴리 도핑 자체가 웨이퍼 전체에 대하여 행하는 것이므로 별도의 마스크는 필요 없다.

Poly Doping이 된 웨이퍼 위에 PR을 코팅 하고, 폴리 마스크를 통해 N-well IMP Masking 떄와 동일 하게

Develop --> Exposure 과정을 통해 UV를 통해 물렁물렁해진 PR을 제거 해 내고 Pattering이 필요 한 부분만 PR을 남기게 하여 후속 Etching 공정에서 Blocking 역할을 해준다.

앞선 과정과 동일 하게, PR Depoisition--> Develop--> Exposure 과정을 통하여 Open 되어 있는 영역에 P+

IMP를 진행 해 준다. 여기선 3족 원소인 P-type 원소를 주입 시켜 Source, Drain 영역을 완성 시켜 준다.

그 후 Diffusion 공정을 통해 표면에만 IMPlanting 되어 있는 P+ 원소를 원하는 깊이 까지 확산 시켜 준다.

반도체 FAB 마다 MOSFET 을 형성 하는 공정이 완전히 똑같지는 않지만, 대략적인 내용으로 Process Flow를 작성 해 보았으니 참고 하면 좋을 것 같다.

수율 개선 엔지니어로 이직을 하기 까지 자기소개서, 면접에 필요한 내용을 정리 해 놓은 전자책이 발간 되었다.

필요 하신 분은 아래 링크에서 참고 하셔도 좋을 것 같다.